# POWER CONSUMPTION MODELING AND ESTIMATION FOR SOFTWARE APPLICATIONS IN MODEL-DRIVEN DEVELOPMENT OF EMBEDDED SYSTEMS

Marco Schaarschmidt

# Dissertation zur Erlangung des Doktorgrades (Dr. rer. nat.) des Fachbereichs Mathematik/Informatik der Universität Osnabrück

Eingereicht am: 27.07.2023 Disputation am: 06.10.2023

| Erste Gutachterin: | Prof. DrIng. Elke Pulvermüller  |

|--------------------|---------------------------------|

| Zweiter Gutachter: | Prof. DrIng. Clemens Westerkamp |

| Dritter Gutachter: | Assoc. Prof. Dr. Hany Elgala    |

# Acknowledgments

Writing a thesis is surely an intense experience. Over the past years, I have had the honor and joy of working with many inspiring, open-minded, and wise people who have always motivated me to keep going and stick to my research ideas. I am very grateful for the help of every one of them.

First and foremost, I would like to express my gratitude to *Prof. Dr.-Ing. Elke Pulvermüller* for supervising this thesis, the trust I received from her, and our discussions over the past few years. I am also grateful for all the scientific and methodical feedback on my work. I also want to thank *Prof. Dr.-Ing. Clemens Westerkamp* for co-advising this thesis and the opportunity to work on many exciting research projects, which helped me stay open-minded as a researcher while maintaining a broad perspective. Next, I want to thank *Assoc. Prof. Dr. Hany Elgala* for accepting the role of the third reviewer.

I extend my deepest gratitude to *Prof. Dr.-Ing. Michael Uelschen* for his trust and support in writing this thesis and the work on scientific publications. It was fun - well, mostly. You never stopped motivating and pushing me toward the end of this thesis. I am also grateful for the valuable discussions and brainstorming sessions about research ideas and problem statements. To use the wording of a computer scientist: I often experienced our conversations as the needed break command to exit the 77 thought loops that have emerged. I truly hope we can continue our research and tackle the following 50 ideas left on our list.

As part of the Software Engineering Lab, I enjoyed working with my colleagues on challenging research projects. I thank *Alexander Grunwald* and *Timo Thurow* for fruitful discussions about physics, electrical engineering, and embedded systems. Next, I would like to thank *Jannis Budde* and *Simon Balzer*, who refined some concepts and provided proof-of-work implementations with their Master's and Bachelor's theses.

Additionally, I want to thank *Lars Huning* and *Michael Spieker* for many fruitful discussions about ideas and concepts related to model-driven development.

Finally, I want to thank my parents, my brother *Robin*, *Stephi*, and *Isabella*, for their endless faith, understanding, motivation, and support through all these years. There have been many ups and downs along the way to this thesis, and I'm fully aware that my mood hasn't always been the best. But let's be clear: This work would not have been possible without you!

A big thank you to each and every one of you!

#### Abstract

Nowadays, embedded systems are ubiquitous and inherent in almost all areas of life. In recent years, trends like the *Internet of Things (IoT)* have been a primary driver for the growing embedded systems market. Many of those IoT devices are battery-powered and more resource-constrained. In addition to economic constraints like total costs and short time-to-market, technical constraints lead to multiple challenges in embedded software development. For battery-powered systems, electrical energy is one of the most critical constraints. For instance, uncontrolled power consumption or an exhausted energy source caused by software applications may lead to failure and costly damage to the device or the environment. Developers often lack knowledge and suitable design concepts to specify, implement, and evaluate energy-efficient software applications. Additionally, constantly changing technologies, extensive functionalities, and various requirements further increase the complexity of embedded software applications while making their development a critical and complex task. To manage the complexity of software applications and the development process, methodologies such as *Model-driven Development (MDD)* have gained importance. However, power-related non-functional aspects are insufficiently considered in MDD.

This thesis addresses the aforementioned gaps and presents a novel framework for energyaware software design patterns. Developers and engineers may use the framework to specify and describe design patterns addressing power-related issues of software applications. The introduced design pattern template provides a set of metrics to describe possible energy savings and the effort-saving ratio when applying a design pattern. The template also contains a unified graphical representation to visualize the effects of design patterns. In addition, a first catalog of energy-aware design patterns is provided, which may be used to design software applications in MDD and traditional development.

To further enhance the development of energy-efficient software applications in MDD, this thesis also introduces a novel power consumption estimation approach for models based on the *Unified Modeling Language (UML)*. The approach is specifically designed for early development stages when optimizations are most effective. A concept for hardware component models is presented, which can be integrated into the software application model. With the provided UML profile, aspects related to power and timing can be modeled. In addition, methods for indirect and direct power analysis are introduced. While the indirect power analysis is based on simulated hardware behavior, the direct power analysis relies on a real hardware platform and a measuring device. Along with the novel and formal description of energy bugs, software applications can be evaluated and energy-related issues detected.

A real-world example of an IoT sensor node and a proof-of-concept implementation of the power consumption estimation approach illustrate the application of proposed modeling and estimation concepts. Moreover, the detection of energy bugs is demonstrated, and the accuracy of the analysis methods is compared. Additionally, the overall performance of the direct power analysis is investigated in depth. The results have shown that the concepts and approaches are suitable for analyzing and predicting the power consumption of software applications in early development phases. Furthermore, the process can be integrated into existing development workflows to support developers using MDD to design energy-efficient software applications.

# Contents

| 1 | Intr | roduction 1                                                                                                                                                  |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1  | Motivation $\ldots \ldots \ldots$            |

|   | 1.2  | Problem Statement and Scope of Research                                                                                                                      |

|   |      | 1.2.1 Research Challenges                                                                                                                                    |

|   |      | 1.2.2 Research Questions and Contributions                                                                                                                   |

|   | 1.3  | Limitations                                                                                                                                                  |

|   | 1.4  | Thesis Outline                                                                                                                                               |

| 2 | Rel  | ated Work and Background 17                                                                                                                                  |

|   | 2.1  | Electrical Power Measurement                                                                                                                                 |

|   |      | 2.1.1 Physical Fundamentals                                                                                                                                  |

|   |      | 2.1.2 Metrics $\dots \dots \dots$                            |

|   |      | 2.1.3 Measurement Techniques                                                                                                                                 |

|   | 2.2  | Embedded Systems                                                                                                                                             |

|   |      | 2.2.1 Architecture and Characteristics                                                                                                                       |

|   |      | 2.2.2 Embedded Software                                                                                                                                      |

|   |      | 2.2.3 Internet of Things                                                                                                                                     |

|   | 2.3  | Software Requirements                                                                                                                                        |

|   |      | 2.3.1 Overview                                                                                                                                               |

|   |      | 2.3.2 Non-functional Requirements                                                                                                                            |

|   |      | 2.3.3 Related Work in the Field of Energy-related Misbehavior                                                                                                |

|   | 2.4  | Software Design Patterns                                                                                                                                     |

|   |      | 2.4.1 Formats and Classification of Patterns                                                                                                                 |

|   | ~ ~  | 2.4.2 Related Work on Power and Energy Aspects of Design Patterns 34                                                                                         |

|   | 2.5  | Model-driven Development (MDD)                                                                                                                               |

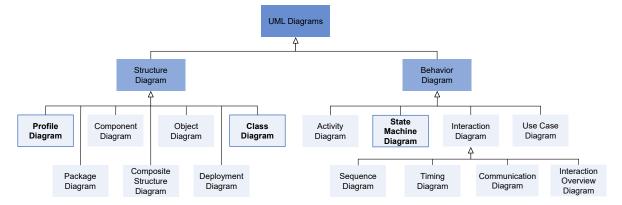

|   |      | 2.5.1 Modeling Languages                                                                                                                                     |

|   | 0.0  | 2.5.2 Model Transformations                                                                                                                                  |

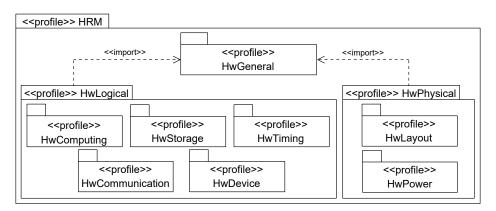

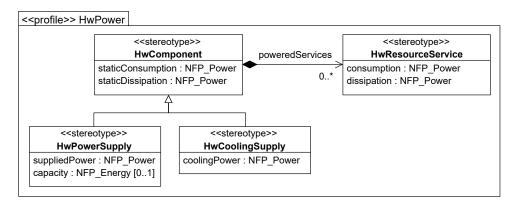

|   | 2.6  | Modeling of Embedded Systems with UML and MARTE                                                                                                              |

|   |      | 2.6.1 Overview $\ldots$ 1 P Cl                                                                                                                               |

|   |      | 2.6.2 Basic Structure and Profiles                                                                                                                           |

|   |      | 2.6.3 Value Specification Language (VSL)                                                                                                                     |

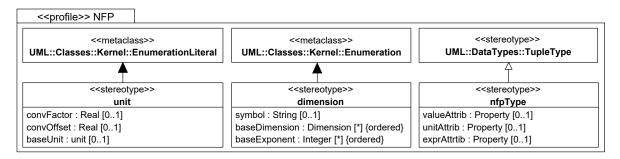

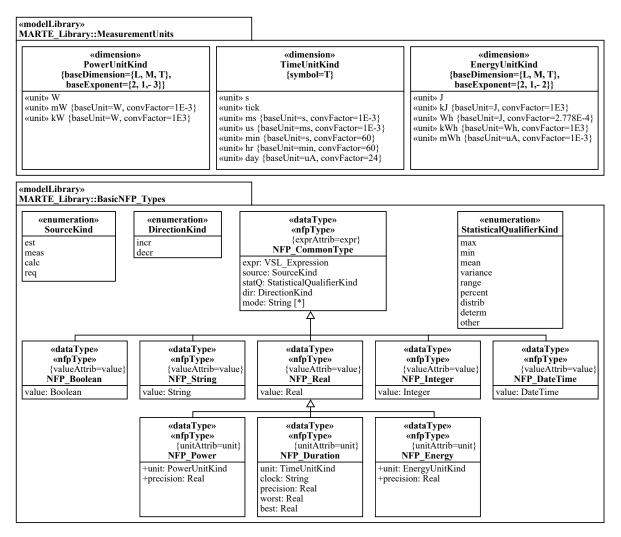

|   | 0.7  | 2.6.4 Non-functional Properties                                                                                                                              |

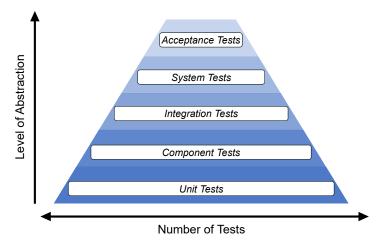

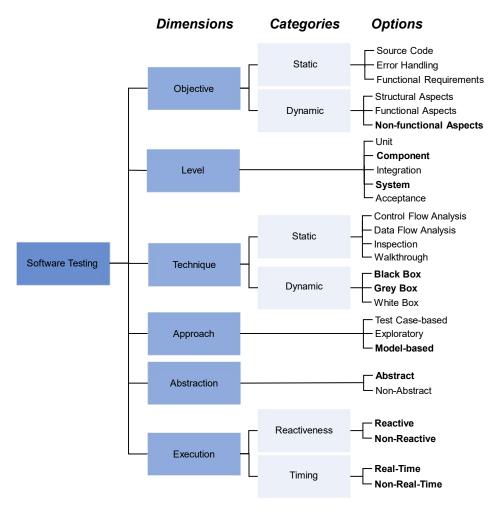

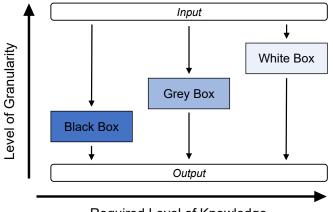

|   | 2.7  | Software Testing Principles                                                                                                                                  |

|   |      | 2.7.1 Dimensions                                                                                                                                             |

|   |      | 2.7.2 Dynamic Testing $\ldots \ldots \ldots$ |

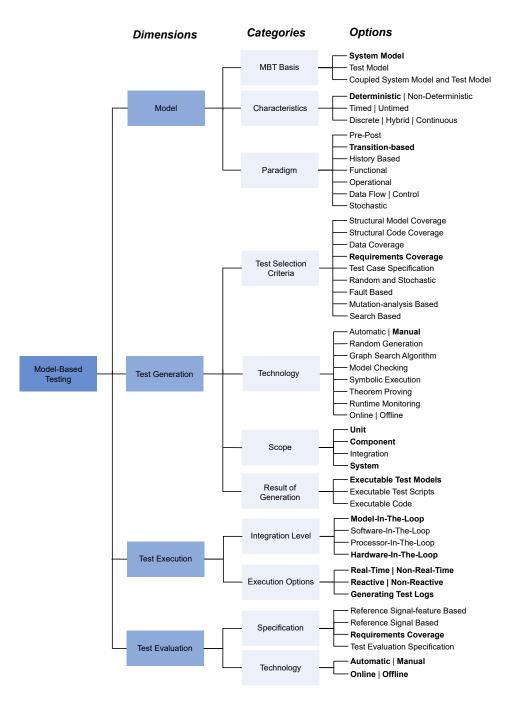

|   |      | 2.7.3 Model-based Testing (MBT)                                                                                                                              |

|          |              | 2.7.4 X-in-the-Loop (XiL) Testing                                                                              |

|----------|--------------|----------------------------------------------------------------------------------------------------------------|

|          |              | 2.7.5 Performance Analysis and Runtime Monitoring                                                              |

|          |              | 2.7.6 Related Work on the Integration of Virtual and Physical Hardware 63                                      |

|          | 2.8          | Related Work on Power Consumption Modeling and Estimation                                                      |

|          |              | 2.8.1 Low-level and Source Code-based Approaches                                                               |

|          |              | 2.8.2 Model-based Approaches                                                                                   |

|          |              | 2.8.3 UML-related Approaches                                                                                   |

|          | 2.9          | Summary                                                                                                        |

| •        | 0            |                                                                                                                |

| 3        |              | rview 77                                                                                                       |

|          | 3.1          | Developer Workflow                                                                                             |

|          | 3.2          | Scenarios                                                                                                      |

|          | 3.3          | Energy Bugs                                                                                                    |

|          |              | 3.3.1 Energy Misbehavior                                                                                       |

|          |              | 3.3.2 Classification                                                                                           |

|          |              | 3.3.3 Example                                                                                                  |

| <b>4</b> | Soft         | ware Design Pattern Framework 89                                                                               |

|          | 4.1          | Introduction                                                                                                   |

|          | 4.2          | Design Pattern Identification Process                                                                          |

|          | 4.3          | Adapted Design Pattern Template                                                                                |

|          | 4.4          | Energy-aware Design Pattern Catalog                                                                            |

|          |              | 4.4.1 Energy-aware Sampling (EAS)                                                                              |

|          |              | 4.4.2 Event-based Computing (EBC)                                                                              |

|          |              | 4.4.3 PowerMonitor                                                                                             |

|          |              | 4.4.4 Direct Memory Access Delegation (DMAD)                                                                   |

|          |              | 4.4.5 Mirroring                                                                                                |

|          |              | 4.4.6 Race-To-Sleep                                                                                            |

| 5        | Dou          | ver Estimation Concept for MDD 115                                                                             |

| 0        | <b>1</b> 0w  | Overview                                                                                                       |

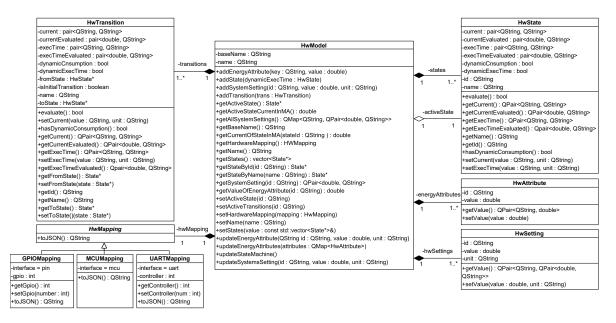

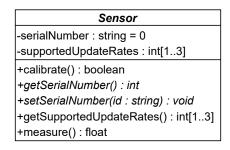

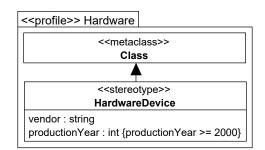

|          | $5.1 \\ 5.2$ | Hardware Modeling         117                                                                                  |

|          | 0.2          | 5.2.1 Characteristics                                                                                          |

|          |              | 5.2.1 Formal Definition of Hardware Component Models                                                           |

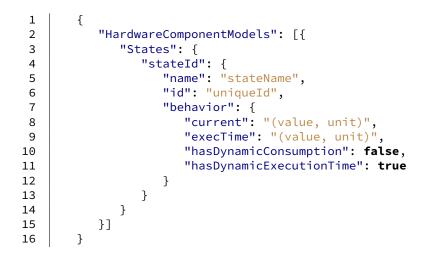

|          |              | 5.2.2 Format Demittion of Hardware Component Models                                                            |

|          | 5.3          | Power Analysis Profile (PAP)                                                                                   |

|          | 0.0          | 5.3.1       Overview                                                                                           |

|          |              | 5.3.2 MARTE Extension                                                                                          |

|          |              | 5.3.3 Hardware Abstraction Package                                                                             |

|          |              | 5.3.4 Hardware Behavior Package                                                                                |

|          |              | 5.3.5 Modeling Dynamic Power-related Behavior                                                                  |

|          | 5.4          | Power Analysis Methods                                                                                         |

|          | 0.4          | 5.4.1       Indirect Power Analysis (IPA)       135                                                            |

|          |              | 5.4.1       Indirect Power Analysis (IPA)       135         5.4.2       Direct Power Analysis (DPA)       136  |

|          |              | $0.4.2  \text{Direct i owel Allalysis (DIA)}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |

| 6             | Pro   | totype  | Implementation                              | 139        |

|---------------|-------|---------|---------------------------------------------|------------|

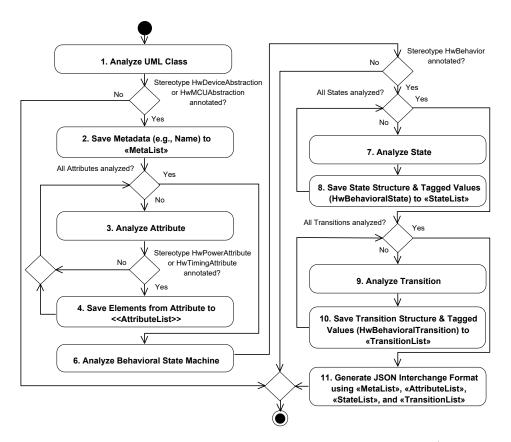

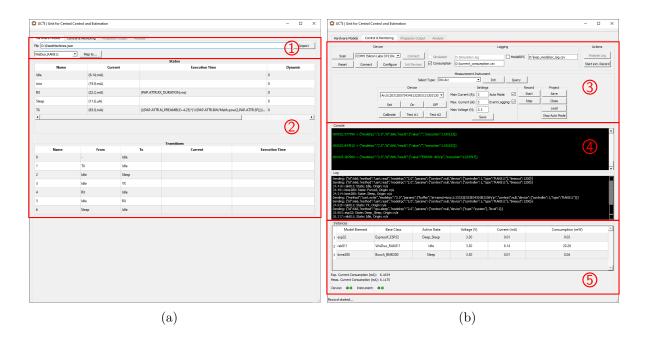

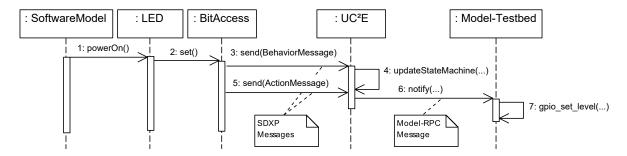

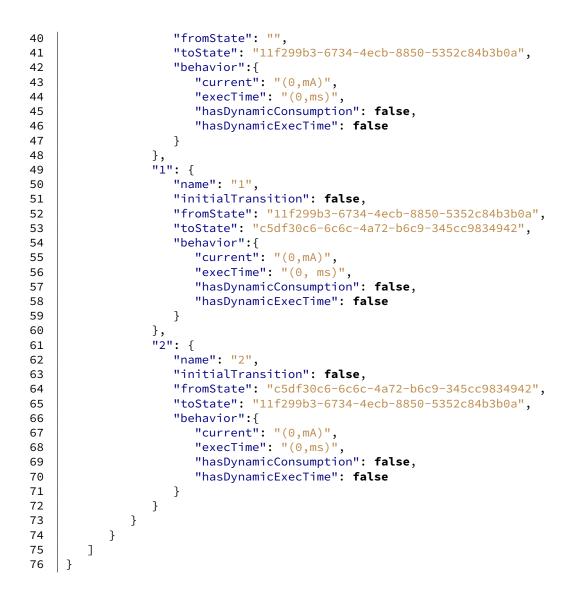

|               | 6.1   | Model   | Transformation                              | . 140      |

|               |       | 6.1.1   | Textual Representation                      | . 140      |

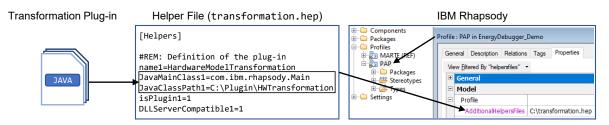

|               |       | 6.1.2   | Enhancement of the MDD Tool                 | . 144      |

|               | 6.2   | Data l  | Exchange                                    | . 145      |

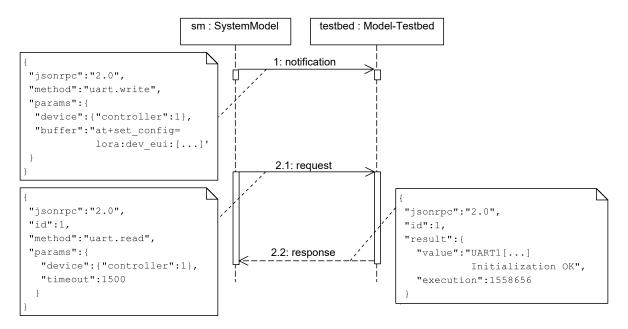

|               |       | 6.2.1   | Simulation Data eXchange Protocol (SDXP)    | . 145      |

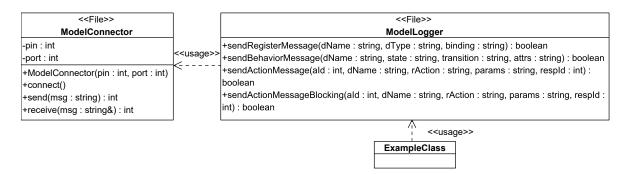

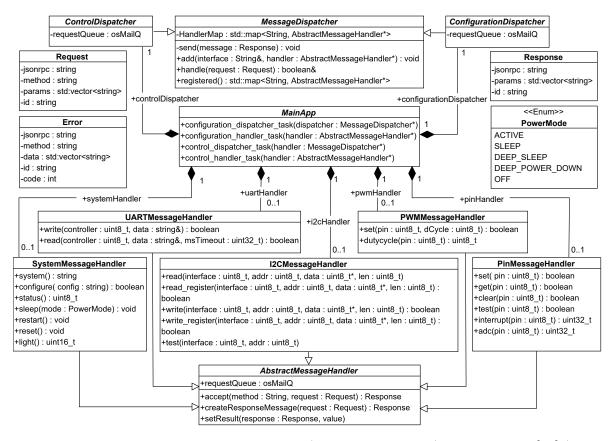

|               |       | 6.2.2   | Messaging Framework                         | . 148      |

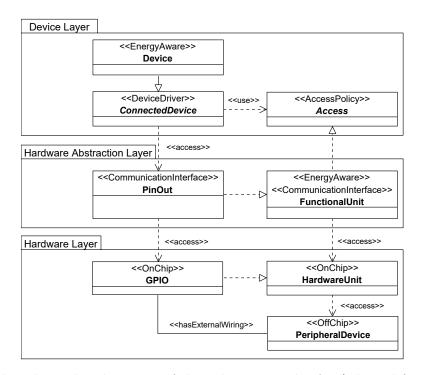

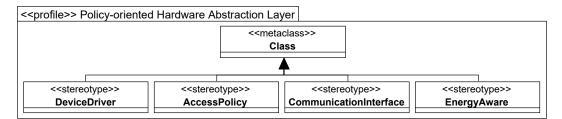

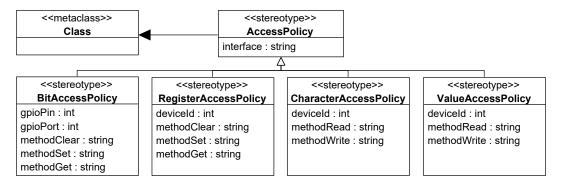

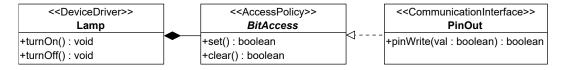

|               | 6.3   | Policy  | -oriented Hardware Abstraction Layer        | . 149      |

|               |       | 6.3.1   | Overview                                    | . 149      |

|               |       | 6.3.2   | Three-layered Architecture                  | . 150      |

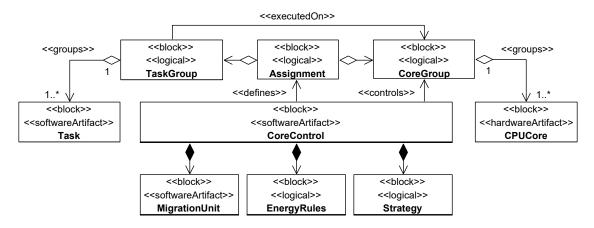

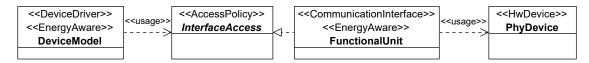

|               |       | 6.3.3   | Model Representation                        | . 152      |

|               |       | 6.3.4   | Application Example                         | . 153      |

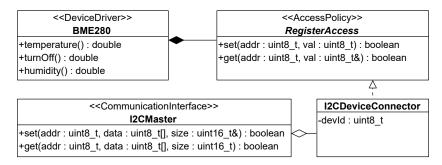

|               | 6.4   | Unit f  | or Central Control and Estimation $(UC^2E)$ | . 155      |

|               |       | 6.4.1   | Graphical User Interface                    | . 155      |

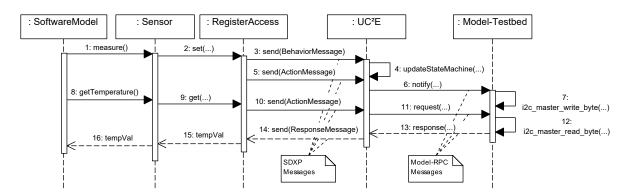

|               |       | 6.4.2   | Communication Principles                    | . 157      |

|               |       | 6.4.3   | Integration of Measuring Devices            | . 158      |

|               |       | 6.4.4   | Power Consumption Estimation                | . 159      |

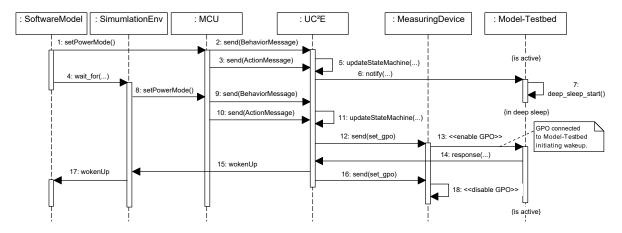

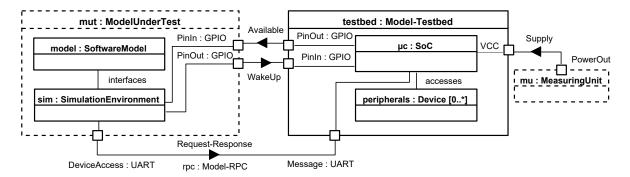

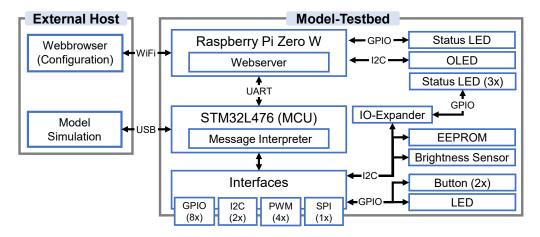

|               | 6.5   | Hardw   | vare-based Model-Testbed                    | . 161      |

|               |       | 6.5.1   | Overview                                    |            |

|               |       | 6.5.2   | Software Layer                              | . 163      |

|               |       | 6.5.3   | Hardware Layer                              |            |

|               |       | 6.5.4   | Model-RPC .                                 |            |

|               |       |         |                                             |            |

| 7             | Eva   | luation |                                             | 175        |

|               | 7.1   | Setup   |                                             |            |

|               | 7.2   |         | Study: Beehive Microclimate Sensor Node     |            |

|               |       | 7.2.1   | Overview                                    |            |

|               |       | 7.2.2   | Hardware Component Modeling                 |            |

|               |       | 7.2.3   | Software Application Modeling               | . 183      |

|               |       | 7.2.4   | Scenario Definition                         |            |

|               |       | 7.2.5   | Power Consumption Estimation                |            |

|               |       | 7.2.6   | Detection of Energy Bugs                    |            |

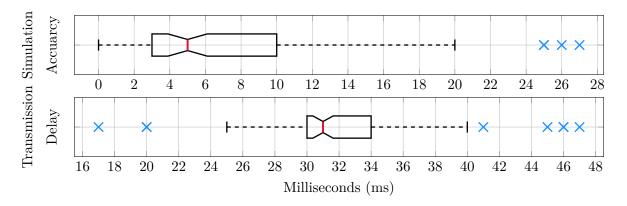

|               | 7.3   | Overa   | ll Performance of DPA                       | . 191      |

|               |       | 7.3.1   | Investigation of Time Delays                | . 191      |

|               |       | 7.3.2   | Power and Timing Tradeoffs                  | . 196      |

| 0             | C     | 1       |                                             | 107        |

| 8             |       |         |                                             | 197        |

|               | 8.1   |         | ary                                         |            |

|               | 8.2   | Outloo  | ok                                          | . 201      |

| Bi            | bliog | graphy  |                                             | 205        |

| Ρı            | ıblic | ations  |                                             | 243        |

| $\mathbf{Li}$ | st of | Acron   | lyms                                        | <b>247</b> |

| Li            | st of | Figure  | es                                          | 251        |

| List o                                      | f Listings                                                 | <b>255</b> |

|---------------------------------------------|------------------------------------------------------------|------------|

| List o                                      | f Tables                                                   | 257        |

| List o                                      | f Symbols                                                  | 259        |

| Apper                                       | ndix                                                       | 263        |

| А                                           | Supplemental Background                                    | . 263      |

|                                             | A.1 Model-driven Architecture (MDA)                        | . 263      |

|                                             | A.2 Tool Support in Model-driven Development (MDD)         |            |

|                                             | A.3 Unified Modeling Language (UML)                        |            |

| В                                           | Complete List of Tags for PAP Stereotypes                  |            |

| $\mathbf{C}$                                | Model Transformation Example                               |            |

|                                             | C.1 Model-to-Text Transformation                           |            |

|                                             | C.2 Model Mapping of Hardware Component Models             | . 277      |

| D Supplementary Information about Model-RPC |                                                            |            |

|                                             | D.1 The configType Object Structure                        | . 279      |

|                                             | D.2 OpenRPC Schema Specification for the UART write Method |            |

| $\mathbf{E}$                                | Supplementary Information about Model-Testbeds             |            |

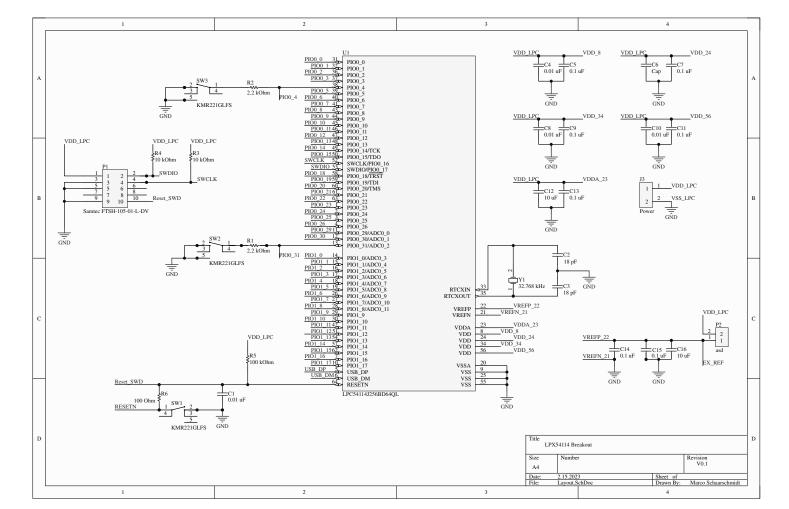

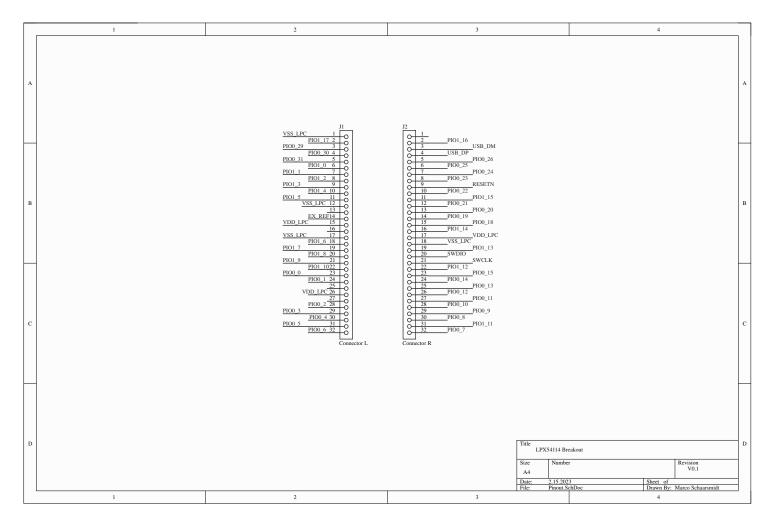

|                                             | E.1 Power Modes                                            |            |

|                                             | E.2 NXP LPC54114 Breakout Board Schematics                 |            |

| $\mathbf{F}$                                | Prototype Implementation Details                           |            |

|                                             |                                                            |            |

# Chapter 1 Introduction

This chapter introduces the field of embedded systems and motivates the need for energyaware software applications. It also discusses how model-based approaches can overcome the challenges of developing energy-aware software applications and explains the importance of considering energy and power-related aspects in the early evaluation. The resulting problem statement is framed by the elaboration of challenges from which this thesis's scope of research and research questions are derived. Furthermore, limitations are discussed, and the structure of this thesis is outlined.

# 1.1 Motivation

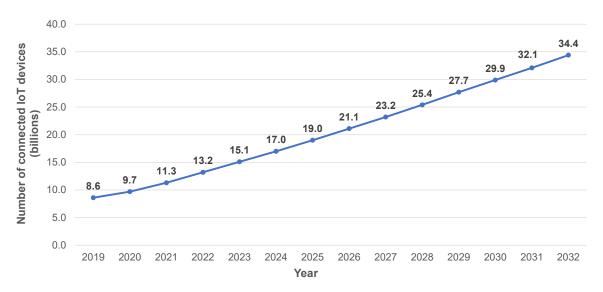

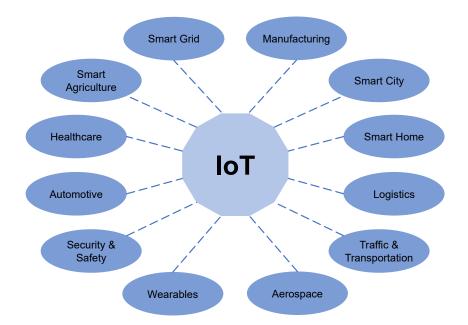

The global market for embedded systems has grown steadily over the past few decades due to the number of different applications. Nowadays, embedded systems are ubiquitous and can be found in domains such as automotive, healthcare, industrial automation, telecommunication, the Internet of Things (IoT), and the Industrial Internet of Things (IIoT). In particular, IoT and IIoT, where embedded systems are used for smart homes, smart cities, agriculture, smart factories, and environmental monitoring, have the highest expected growth [2, 105, 423]. Researchers assume a continuing expansion of IoT devices over the following years. A study proposed in [400] expects an increase from 8 billion devices in 2020 to more than 25 billion by 2030. The authors of [80, 401] forecast IoT devices to represent 50 % of all networked devices in the year 2023 using short-range technologies, such as Wi-Fi, Bluetooth, and Zigbee. In a study released by Transforma Insights [257], an increase from 13.2 billion IoT devices in 2022 to 34.4 billion in 2032 is expected, corresponding to an annual growth rate of 10 %. Friedli et al. (2016) [126] estimate the number of mains-powered IoT devices in categories such as smart appliances, roads, lighting, and home assistants to reach 5.7 billion by 2025, with an expected standby power consumption of 46 TWh. The number of battery-powered IoT devices is expected to reach 23 billion units in the same year [395]. In addition, the trend toward more electric-powered devices across all sectors and the change to alternative energy sources raise the risk of power outages. This affects the overall availability of electrical power, making it an increasingly important resource. As energy prices continue to rise [416], the power consumption of these devices becomes a critical design constraint.

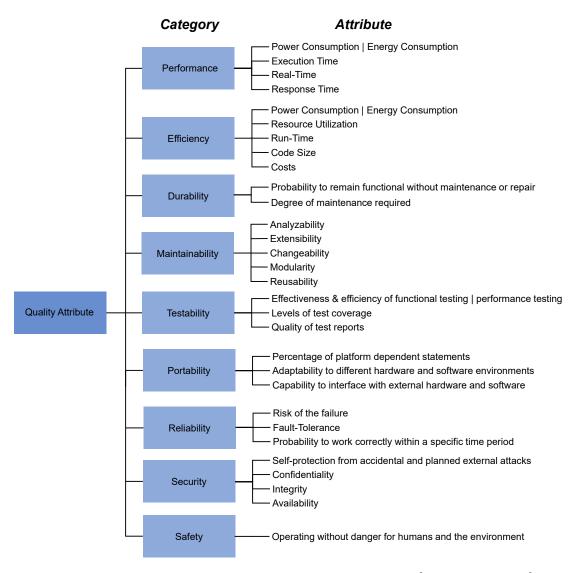

Embedded systems are generally resource-constrained, especially for domains relying on low-power systems such as IoT. In addition to general economic-related constraints like total costs and short time-to-market, functional safety and technical constraints such as the processing power, memory size, or battery capacity lead to multiple challenges in software engineering. Supplementary to the mentioned constraints and the increased functionality of modern software applications, software developers and engineers have to deal with the growing complexity of embedded system designs at a low level due to the variety of processor architectures, communication interfaces, and the growing number of proprietary hardware with distinct functionalities. Especially for battery-powered IoT devices, energy and power-related *Non-functional Requirements (NFRs)* for hardware and software need to be defined at the beginning of the development since the battery capacity is one of the most critical factors for the operational lifetime of the device. The supply of power can be a major challenge if those devices are placed in harsh environments or buried underground [146, 409]. From an economic and technical perspective, replacing or recharging the power source for these devices is often either impossible, impractical, or results in higher costs.

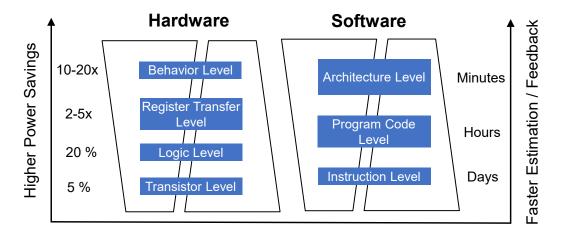

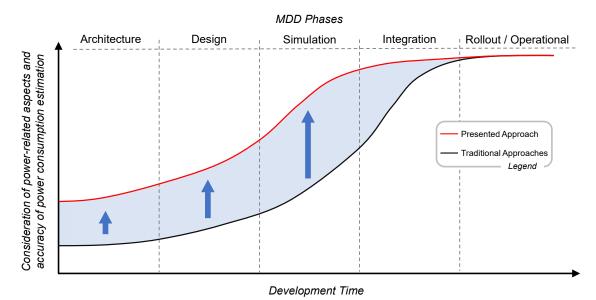

Although energy consumption is an invisible property, it can be a significant bottleneck of embedded systems [35]. Up to 80 % of the total energy consumption is generated by the software application [231] since it drives and controls hardware components and, thus, directly affects the energy-related behavior of the systems. In the past, energy and power consumption aspects were addressed primarily at the hardware level, resulting in more energy-efficient hardware components. So far, little attention has been given to the software layer that controls and directs most hardware activities. In fact, as a property of hardware components, the static energy demand can be addressed by improved hardware designs. In contrast, optimizing the software application can address the dynamic energy demand during runtime. Energy awareness is often completely ignored in the software development process [123] because developers and engineers may be unaware of the causes of high energy consumption and lack knowledge of how to reduce the energy impact of software applications [38, 289, 301]. Since the impact of the software application on energy consumption is often unknown, it is essential to consider power-related NFRs in early design phases, where changes are more effective [375]. However, even if the definition of NFRs related to energy and power in early development phases prompts developers and engineers to design energy-efficient software applications, the traditional software development process is not designed to address such NFRs at an early development stage. The software development process typically focuses on functional aspects, while non-functional aspects are tested and evaluated later in the development cycle. At this point, the software application and hardware platform are close to their final states, and the software application can be executed on the embedded system. Addressing non-functional issues such as power consumption, energy efficiency, and real-time in later development phases may lead to extensive re-design and re-implementation phases if changes at the software architecture level or requirements level are needed [33]. These processes may extend the development time and lead to higher costs, schedule delays, lost productivity, damaged customer relations, or missed market windows [361]. In addition, no approaches or tools exist for estimating the power consumption and detecting potential power-related misbehavior of software applications in early development phases where the target hardware platform may not be available or defined.

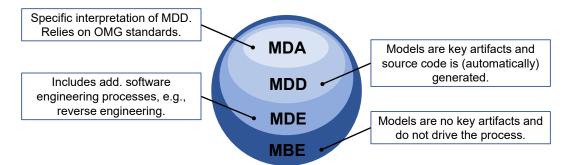

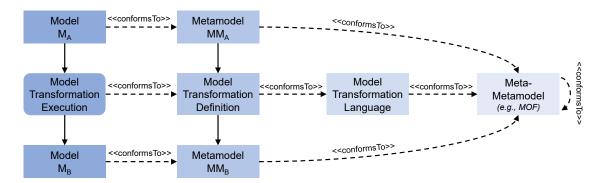

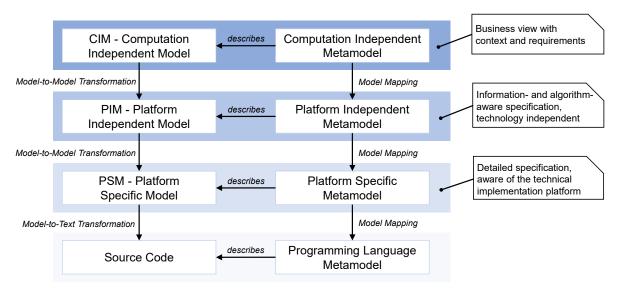

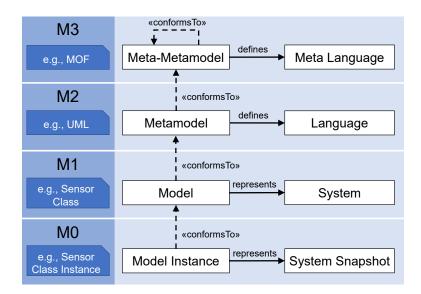

Indeed, model-driven approaches offer the opportunity to address and improve software quality in early development phases [292]. As previous paradigm shifts in embedded software engineering have led to higher levels of abstraction, approaches such as *Model-driven Development (MDD)* for designing and developing software applications have received more attention. MDD uses models and modeling techniques for the software development process to not only achieve higher levels of abstraction but also to manage the complexity of software applications,

e.g., for embedded systems. Furthermore, MDD also increases the formalization of software development activities and tasks so that processes can be automated [152, 369], which also raises productivity [193]. Such automation allows developers and engineers to focus on the application logic, behavior, and program flow of software applications and helps overcome the challenges of the development process [56, 326]. Due to the formalization, models can be exchanged between domains and reused with concepts like model-to-model and model-to-text transformation, which increases developer productivity even further. Additionally, MDD enables an evaluation of requirements at the architecture level in early stages of the development process, e.g., using *Model-based Testing (MBT)* techniques. Exemplary for software applications used in airplanes, [153] compared an architecture-modeling approach with existing development paradigms and found that 70 % of the software defects are located at the requirement or design level. While more than 50 % were identified during the hardware/software integration as part of later development phases, less than 10 % of these defects were detected in their respective phases. Due to this, the rework costs were 100 times higher than the costs for correcting the errors at the levels they occurred.

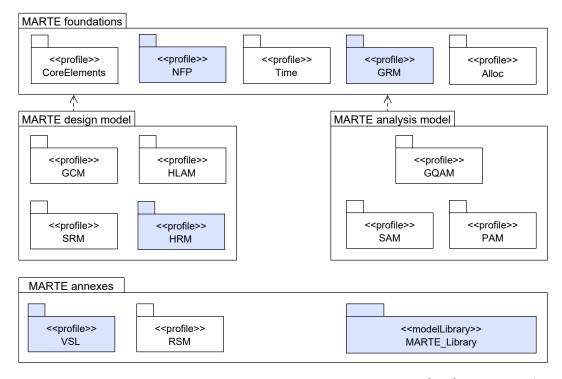

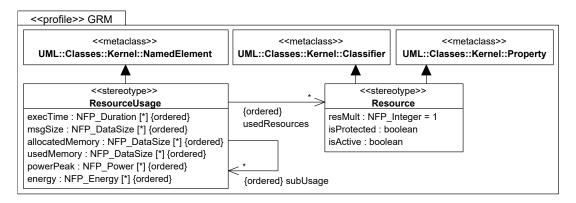

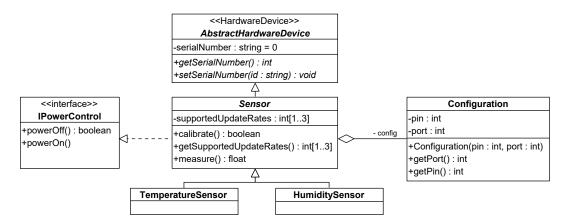

McKinsey [92] confirms the increasing complexity of software development within embedded systems and suggests the consequent application of *Domain-driven Design (DDD)* and a ubiquitous language. As a ubiquitous language, the Unified Modeling Language (UML) [275] may be used by both DDD and MDD [114]. As the most used modeling language in the embedded software industry [7], UML provides concepts for object-oriented modeling of structural and behavioral aspects of software applications and provides graphic notation techniques so that software developers can focus on the application design, behavior, deployment, and program flow. Additionally, with UML profiles, UML provides a generic extension mechanism to include domain-specific concepts in the definition of models using stereotypes, tag definitions, and constraints. Existing notations and specifications may be considered to introduce energy awareness in UML. The Modeling and Analysis of Real-Time and Embedded systems (MARTE) UML profile [278] extends the UML and provides a set of modeling concepts, data types, and notations to support the modeling and analysis of real-time and embedded systems. MARTE also enables the modeling of Non-functional Properties (NFPs), such as timing constraints, performance, and schedulability, as well as basic power consumption and dissipation aspects as static values.

It is crucial to consider both static and dynamic power and energy consumption aspects for an energy-efficient system. Since the software application is responsible for hardware activities during runtime, the advantage of addressing the software application to reduce the (dynamic) energy consumption of an embedded system is obvious. In conjunction with the fact that changes and optimizations of the software application are considered to be more effective at higher levels of abstraction [375], design flaws and behavioral issues should be identified early in development to minimize costs and development time. This is especially true for energy- and power-related issues, which, as noted earlier, are typically discovered in later phases of the development process. Although many efforts in the research areas of software engineering and software development address energy-efficient software applications and energy-aware development, there are still a number of unresolved high-potential topics. In software engineering, for instance, such topics include the exploration of suitable design concepts, models, patterns, and strategies to address energy- and power-related aspects [38]. MDD, however, lacks concepts, methods, and tool support for estimating power-related nonfunctional aspects in early design and development phases. These unresolved topics will be addressed within this thesis and further elaborated in the next section.

# **1.2** Problem Statement and Scope of Research

As motivated in the previous Section 1.1, developing software applications for embedded systems is a challenging task. In addition, developers and engineers have to deal with the increasing complexity of embedded software applications caused by highly dynamic and constantly changing technologies, extensive functionalities, protocols, and requirements [49, 282, 292, 369]. Especially for low-power and battery-powered embedded systems, energy and power efficiency are the most critical quality attributes determining the operational lifetime of the device, which has to be addressed by engineers and developers. This also implies that software applications play a central and critical role. For instance, the system will fail if the energy source is exhausted too quickly due to a non-optimized software application or uncontrolled energy consumption, which may result in costly damage, e.g., a loss of the device or harm to the environment [202]. Regarding power consumption, *Steve Furber*, the designer of the original ARM microprocessor, stated in an interview in 2010 [60]:

"If you want an ultimate low-power system, then you have to worry about energy usage at every level in the system design, and you have to get it right from top to bottom, because any level at which you get it wrong is going to lose you perhaps an order of magnitude in terms of power efficiency. The hardware technology has a first-order impact on the power efficiency of the system, but you've also got to have software at the top that avoids waste wherever it can. [...] Do programmers really have any understanding of how much energy their algorithms consume?"

This statement underlines the importance of optimization and evaluation at higher levels of abstraction, e.g., the software architecture level, where changes are expected to be most effective [143, 375]. This is also confirmed by researchers who argue that energy consumption needs careful consideration [35] and should be studied across all software development phases [123]. Understanding the impact of the software application on properties such as power consumption and execution time requires developers to have in-depth information on behavioral aspects of the software application, in particular hardware-software interactions. The availability of energy-efficient hardware components indicates that power consumption is well-addressed by developers and researchers at the hardware level. However, little attention has been given to the software level that controls and directs most hardware activities, and the energy-related impact of software applications is often unknown. In [38], the authors stated that "[m]ost architects and developers are unaware of energy efficiency as a quality attribute of concern, and hence do not know how to go about engineering and coding for it. More fundamentally, they lack an understanding of energy efficiency requirements". This statement highlights important research gaps in energy-aware software engineering. For instance, new concepts have to be developed to enhance the understanding of energy efficiency requirements, how they are derived, and how they relate to software and system behavior. Developing energy-efficient software encompasses many aspects of software development. This includes the optimized use of compilers and (object-oriented) programming languages and the optimization of the software architecture and behavior, e.g., the interaction between software modules and hardware components. In software engineering, design patterns, as proven best practices, might be used to overcome the complexity of applications and address energy-efficiency aspects. However, there is an ongoing lack of suitable design concepts such as tactics or patterns [38]. Additionally, and to the best of our knowledge, only limited work towards software design

patterns exists, which directly describes the effect on energy efficiency and power consumption when applied to the design of software applications.

With MDD as the main methodology used in this thesis, the software development process is mainly driven by the use of models. Consequently, the consideration of power-related aspects should be part of the MDD process and based on the defined models. Quantitative results obtained by evaluations during the MDD process may be used to adapt the software architecture and design to fulfill energy- and power-related NFRs already in early development phases. Since the impact of software applications depends highly on the hardware platform, an analysis of NFRs, especially for power- and energy-related aspects, is typically carried out by engineers and developers in later development cycles where the software application and the hardware platform are more advanced and functional testing has been completed [235, 260, 367]. To still be able to perform early evaluations of, e.g., power constraints, a suitable energy model has to be developed [35]. Additionally, to execute performance evaluations w.r.t. energy and power consumption aspects, concepts to simulate and analyze the behavior of software application models must be supported by MDD tools and integrated into the development workflow of developers and engineers. Commercially available MDD tools such as MathWorks MATLAB [380], MathWorks Simulink [383], and IBM Engineering Systems Design Rhapsody – Developer<sup>1</sup> [164] provide simulation environments and support the execution of model-based test cases. Additionally, concepts and extensions for MathWorks MATLAB [382] and IBM Rhapsody [165] exist, providing techniques to execute test cases on, e.g., embedded systems. However, the evaluation provided by the aforementioned MDD tools is focused on functional aspects of software applications and lacks support to analyze and evaluate NFRs. Even while not directly mentioning MDD, Steve Furber also addresses the lack of tool support during his interview [60]:

"[...] programmers will not be able to afford to be ignorant about the energy cost of the programs they write. [...] You need tools that give you feedback and tell you how good your decisions are. Currently the tools don't give you that kind of feedback."

Currently, the evaluation of embedded software applications in MDD requires the integration of platform-specific source code. Moreover, it is based on repetitive steps, including manual effort such as editing, compiling, and flashing the auto-generated source code for one or multiple targets if, for instance, the most suitable system components, e.g., as sensors or actuators, should be identified. This process is also denoted as *edit-cross-compile-flash-debug* cycle [30, 393].

Besides the lack of tool support, the direct execution and evaluation of software applications on target hardware platforms is part of later development phases when prototypes are available. In early development phases, however, frequent hardware component changes still occur. The effort necessary to evaluate non-functional aspects in this manner may result in a bottleneck of the development process and may cause additional time delays and costs. This can be compensated by a faster evaluation process in early phases, which may include, e.g., rapid prototyping principles. It is essential to have a proper set of methods and tools that help software developers in early design phases. These tools should enable the evaluation of software applications regarding power-related NFRs by estimating the power consumption and detecting possible power-related misbehavior. To the best of our knowledge, in MDD, no approach exists for an early and straightforward power consumption estimation of software

$<sup>^{1}</sup>$ To improve readability, the abbreviation *IBM Rhapsody* is used in the following chapters of this thesis.

applications. Additionally, since embedded systems in domains such as IoT typically consist of multiple sensors, actuators, and at least one communication interface, the power consumption estimation approach should encompass the entire system.

With the right concepts, methods, and tools, developers and engineers are fully aware of the software application's system-wide energy footprint. They may be able to design and evaluate energy-efficient software applications in an enhanced manner. Accordingly, the following thesis statement emerges from considering open research subjects and the aim of this thesis.

**Thesis Statement:** "Developers and engineers are able to design energy-efficient software applications and evaluate energy-related requirements in early development phases of MDD if appropriate best practices exist and powerful analysis methods with tool support are provided."

The challenges resulting from the problem statement are addressed in the following Section 1.2.1. The research questions derived from the identified challenges are presented along with the scientific contributions of the thesis in Section 1.2.2.

## 1.2.1 Research Challenges

Modeling and estimating a software application's impact on the overall system's power consumption is challenging, especially in early development phases, where the prototype hardware platform may not be available or defined. Different challenges exist along the way to achieve a power consumption estimation workflow for software applications in MDD, which can be grouped into four broad categories:

#### Challenge 1: Definition of Power- and Energy-related Requirements

The description and differentiation of correct and faulty power- and energy-related behavior is crucial for testing and evaluating the NFPs of embedded systems and, simultaneously, a complex and challenging task due to the unique characteristics of these systems. Effective testing and evaluation of power- and energy-related behavior requires a specific and more formal definition of NFRs to determine whether the intended behavior meets the expectations. In [34, 293, 295], a broad classification and definition of power-related misbehavior for certain domains and device classes, e.g., smartphones, are provided. For example, Banerjee et al. (2014) [34] mentioned that power-related misbehavior denoted as *suboptimal resource binding* is defined as "binding resources too early or releasing them too late causes them to be in [a]high-power state longer than required". These and similar statements are primarily formulated in a natural language, while a formal definition of such energy and power-related misbehavior is missing. For the rest of this thesis, energy and power-related misbehavior are referred to as energy bugs. A formal definition of energy and power-related NFRs would have a strong interrelationship with energy bugs, where one may be derived from the other. In addition, such a formal definition may significantly contribute to automatic analysis. It is not known how to formally define energy and power-related NFRs and describe energy bugs so that they can be interpreted and processed by both humans and machines.

### Challenge 2: Best Practices of Energy-aware Design

When developers and engineers address power-related issues during software application design and implementation phases, the availability of documented best practices is essential to implement the most appropriate solution. Such paradigms are typically referred to as *software*  design patterns. By using structural, creational, and functional design patterns, developers and engineers can optimize and improve the software application in early phases while avoiding time delays and increasing costs due to additional re-design and optimization cycles. However, existing design pattern templates do not provide categories or fields to address non-functional aspects such as power and energy consumption. To be able to calculate and estimate the effects of a software design pattern, a design pattern template is needed to describe such energy-aware software design patterns uniformly. With a focus on non-functional aspects, such a uniform description allows the developer to compare the effects of different design patterns without having to implement and test each variation and select the most suitable design pattern with the highest positive effect.

#### Challenge 3: Design and Modeling of Power-related Properties

To model power-related aspects of the software application in MDD, properties of hardware components and their dynamic behavior must be considered. Approaches found in the literature and discussed in Section 2.8 (p. 65 ff.) lack the capabilities to combine those power-related aspects with the software application model. However, while focusing on the software perspective, the integration is necessary to consider the software application's dynamic behavior during simulation or execution and hardware-software interactions for the analysis process. So far, it is unknown how software application models can be extended and which techniques are suitable to model power-related aspects in MDD. The additional effort to model power-related aspects should not force software developers to lose their focus on the software design and their actual workflow of the software modeling process. Furthermore, power-related model components must be integrated into the software model without the need to adapt existing structures or restrict intended functionalities. They also have to be removed before the final source code is generated. Therefore, the challenge is to define a lightweight extension for software application models which can be used to estimate power consumption.

## Challenge 4: Simulation and Evaluation of Software Application Models with integrated Energy Models

For the evaluation in early development phases, the simulation of software application models is a significant aspect. By performing simulations as early as possible during development, developers may identify problems that would otherwise remain undetected and become visible in later phases, e.g., field tests. While some tools in the MDD domain offer a simulation environment for evaluation, they focus on functional aspects and do not support an evaluation of non-functional aspects. Furthermore, the hardware behavior must also be part of the simulation environment to reflect hardware-software interactions. So far, no method exists to include power- and energy-related non-functional aspects in the simulation or execution of software application models. Besides the simulation, the analysis of NFRs is also not addressed by current MDD tools. Instead, the analysis is carried out and performed in later development stages, where the time and effort needed to address the misbehavior is significantly higher. However, it is unclear how the analysis may be performed during early modeling. Besides defining concepts for the evaluation process and verification mechanisms, an analysis tool has to be developed which can be integrated into the MDD process. For a proper analysis, an optional solution would be aware of all hardware models and hardware accesses initiated by the software application. Due to the lack of support from MDD tools, the evaluation process must be executed separately, e.g., based on simulation logs. A more promising but

non-trivial approach would be to interconnect the simulation environment with the analysis tool to realize runtime monitoring, which also requires proper instrumentation for a power consumption estimation.

# 1.2.2 Research Questions and Contributions

To address the challenges introduced in Section 1.2.1, the following Research Questions (RQs) have been derived, focusing on the engineering and evaluation of software applications in the early development phases of MDD.

**RQ1** – Formal Definition of Energy-related Behavior and Defects: *How should non-functional requirements for energy-related behavior be described?*

Defining a clear and comprehensive set of NFRs is essential when designing energy-aware embedded systems. During the design phase, it is important to precisely describe the expected energy-related behavior so that developers are able to make comparisons during testing and automate the evaluation process. RQ1 is related to *Challenge 1*.

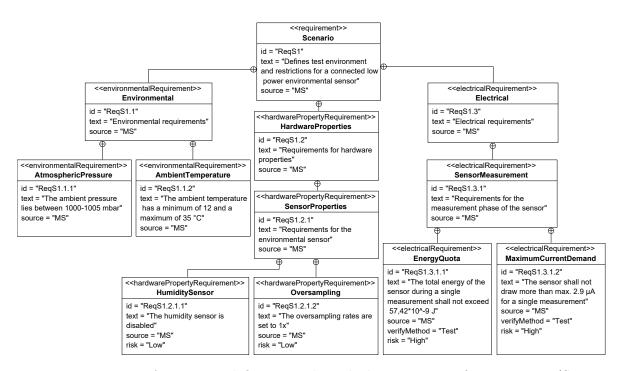

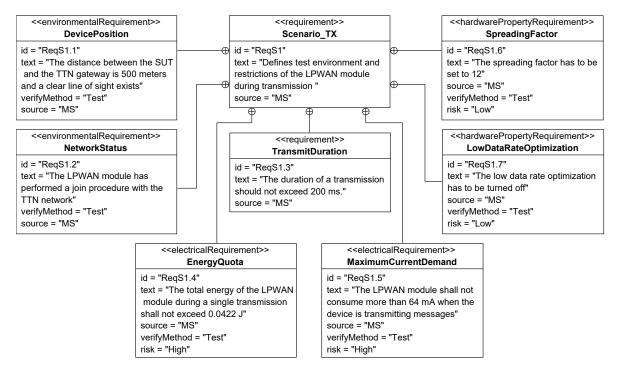

The following contributions to address RQ1 provide fundamental concepts as a basis for further approaches presented in this thesis. A novel formal description of NFRs is presented to accurately specify the expected energy-related behavior of an embedded system. Additionally, a formal specification of *energy bugs* as the description of power-related misbehavior w.r.t. embedded systems is provided. While the specification of energy-related NFRs and the description of energy bugs as violations of such NFRs share the same underlying metrics, power-related misbehavior may be detected and classified during testing. Furthermore, a precise specification of the environment and system properties by a set of conditions and constraints has been elaborated to describe the range of validity of both NFRs and energy bugs when executing test cases. The contributions are published in [341] and may be summarized as follows:

- The introduction of the two metrics, energy quota  $E_{qu}$  and the maximum current demand  $I_{dmax}$ , for the formal description of power- and energy-related NFRs and for the specification of boundaries for an energy bug-free system or subsystem. Due to the formal definition of energy bugs, they can be expressed using the same metrics. This enables developers to perform a power analysis and evaluation of NFRs and facilitates the application of automated processes.

- A novel and more comprehensive classification of energy bugs independent of specific device types. The presented classification categorizes energy bugs based on their characteristics and origin, e.g., hardware and software layers.

- The concept of scenarios as a set of conditions and constraints to specify aspects of the environment and the system for the execution of test cases that apply for a specific amount of time. As a modeling approach of the environment and the context for testing, the concept of scenarios also addresses RQ4.

**RQ2** – Best Practices and Design of Energy-aware Software Applications: What are the best practices for energy-aware software applications, and how can they be uniformly described and formalized as design patterns?

This RQ is related to *Challenge 2* and addresses the problem of how aspects related to power and energy consumption as NFPs of a system may be considered when designing software applications. Furthermore, RQ2 aims to investigate whether design patterns for software applications focusing on power and energy consumption can be described uniformly so that software developers can identify and apply best-practice solutions for their problems.

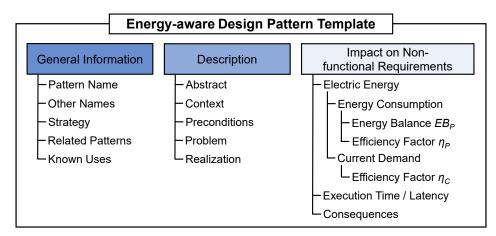

By applying energy-aware software design patterns, it is expected that the misbehavior of software applications may already be addressed at an early stage of development. The idea to address RQ2 is to provide software developers with a catalog of behavioral design patterns for software applications as reusable paradigms at the design and architecture level, focusing on power-related aspects. For this, a novel framework has been defined to identify and describe energy-aware software design patterns. The contributions are published in [337, 338, 392] and may be summarized as follows:

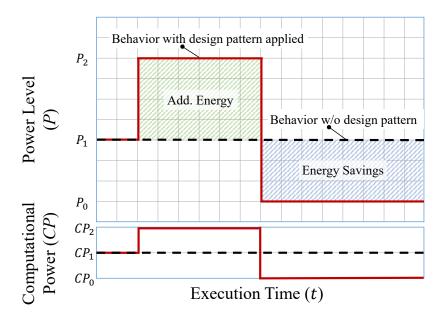

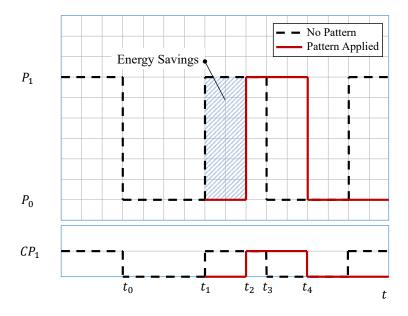

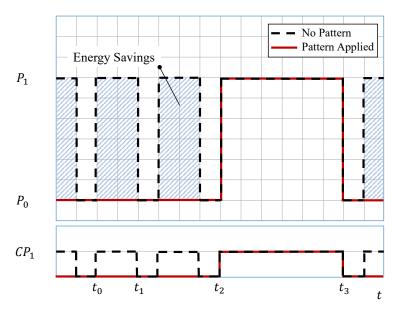

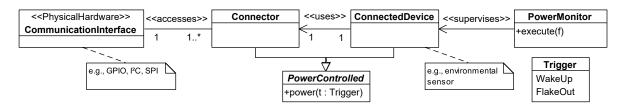

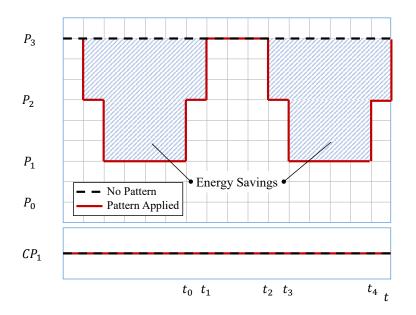

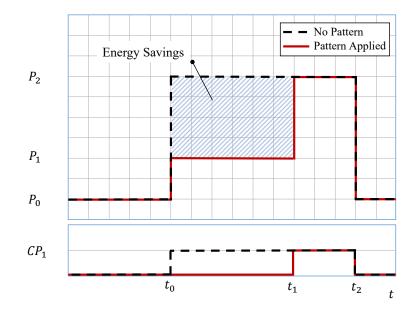

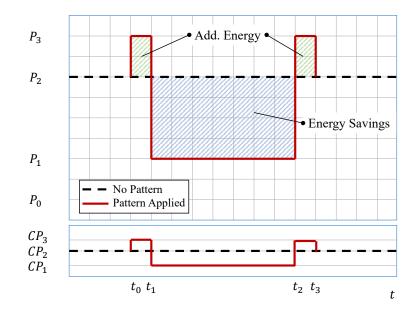

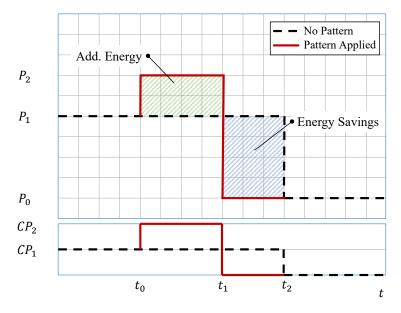

- The development of a novel framework and a design pattern template for the identification and uniform description of software design patterns. The design pattern template introduces a new section to address the impact and side effects on NFRs, the two metrics energy balance  $EB_P$  and efficiency factor  $\eta_P$ , and a uniform graphical representation to outline the power-related and computational behavior of design patterns.

- A catalog of energy-aware design patterns to demonstrate and prove the applicability and expressiveness of the framework. The catalog contains novel and existing design patterns from different areas of software and hardware development.

**RQ3** – Joint Modeling of Functional Software Application Models and Energy Behavior: How can software application models be extended with energy-related hardware characteristics to make the software-related impact visible and traceable?

RQ3 addresses *Challenge 3* and aims to discover concepts and mechanisms for enhancing software application models to make energy-related features visible during analysis. Additionally, RQ3 refers to the necessary level of detail and characteristics when modeling hardware components and how they may be seamlessly integrated into the software application model.

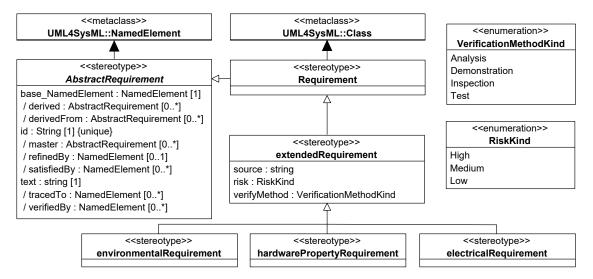

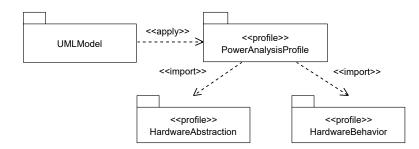

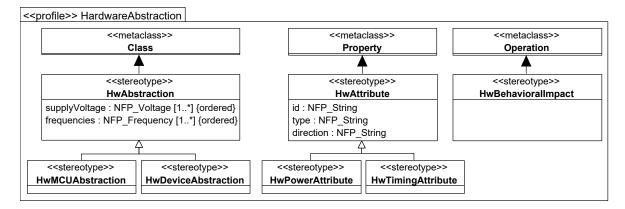

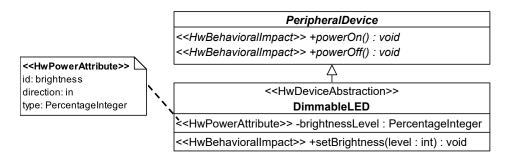

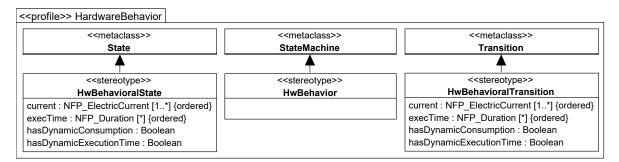

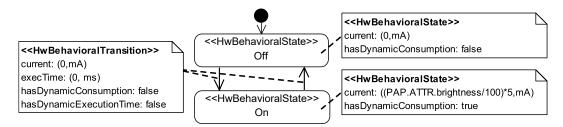

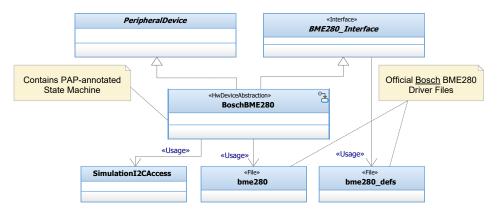

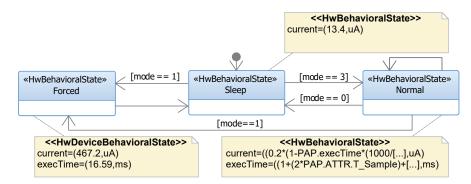

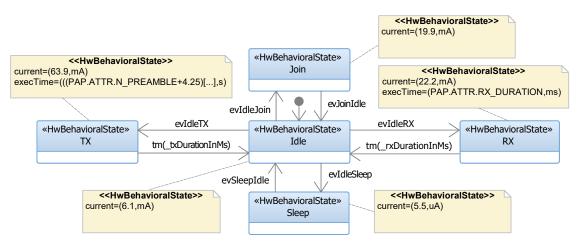

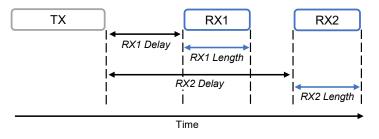

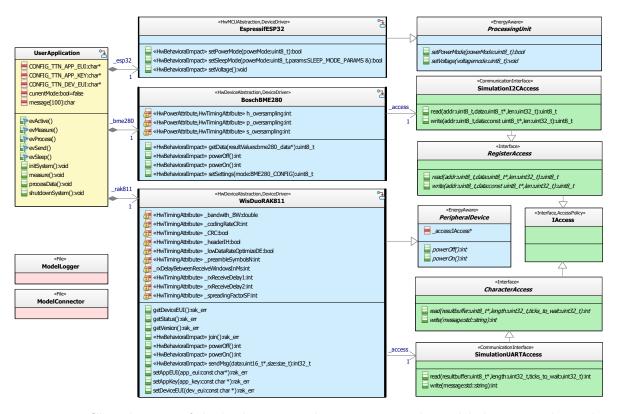

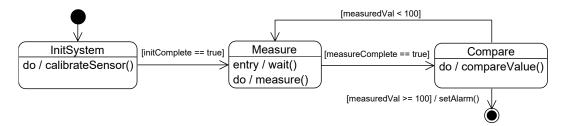

To model power-related aspects of the system, a description of hardware components and their power-related behavior is required. For this, a specification of *hardware component models* is introduced, which also incorporates an *energy model* to specify the temporal powerrelated behavior of a hardware component model. For the description of power-related aspects, the novel *Power Analysis Profile (PAP)* is introduced as a domain-specific customization of UML to provide an energy-modeling and, e.g., to integrate the concepts of energy models for UML state machines. For this, the PAP provides additional stereotypes and tagged values to specify, for instance, the electric current consumption and execution time. Since the concept of hardware component models can be mapped to UML elements, e.g., by the aid of the PAP, a seamless integration into the software application model can be performed, resulting in a *system model* which addresses RQ3. The main contributions are published in [336, 339, 340, 341, 391] and can be summarized as follows:

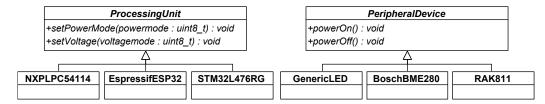

- A novel system-wide modeling approach based on hardware component models covering *Microcontroller Units (MCUs)* and connected peripheral devices.

- A UML-based description of hardware components that can be combined with a software application model to define a system model. Composed of an energy model as a UML state machine for energy-related non-functional aspects and a UML class for functional aspects, hardware component models provide interfaces for their utilization by software application models in MDD.

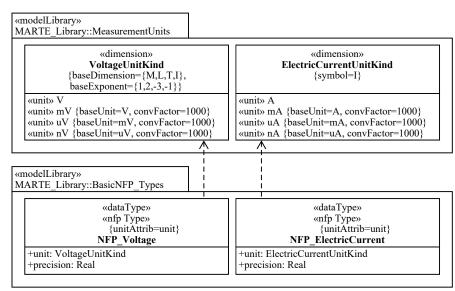

- The PAP UML profile to model energy-related aspects. The UML profile is based on the MARTE profile and provides stereotypes to extend hardware component models and introduces new data types to describe the electric current and voltage as NFPs.

**RQ4** – Early Evaluation of Energy-aware Software Applications in MDD: *How* can the energy-related impact of software application models be determined, and energy-related misbehavior be identified when the hardware platform is not available or only partially available?

The execution of software application models is based on simulations. Since MDD tools and simulation environments differ strongly w.r.t. their general functionality, an external analysis process has to be developed. For the evaluation of energy-related aspects, concepts to cope with the different conditions in early development stages have to be defined.

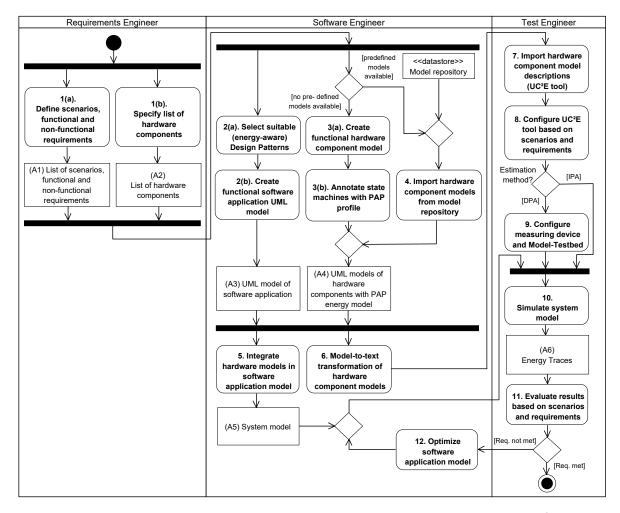

To answer RQ4 and overcome *Challenge 4*, the MDD tool used in this thesis is enhanced to transform hardware component models for a tool-independent approach. The simulation environment of the MDD tool has also been extended to allow data exchange with external analysis tools during execution. Moreover, power analysis methods have been developed for the early evaluation of energy-aware software applications in MDD. The main contributions to address RQ4 are published in [339, 340, 341] and may be summarized as follows:

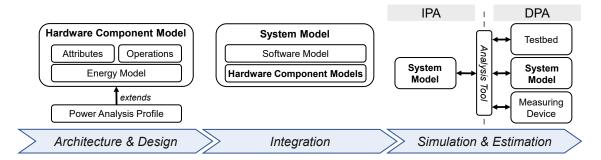

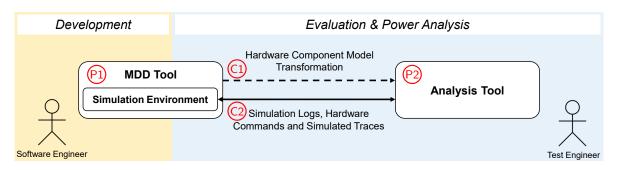

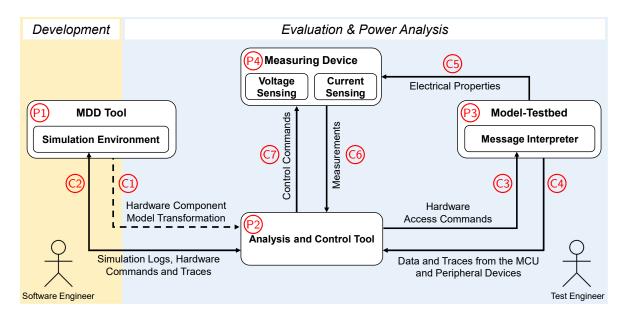

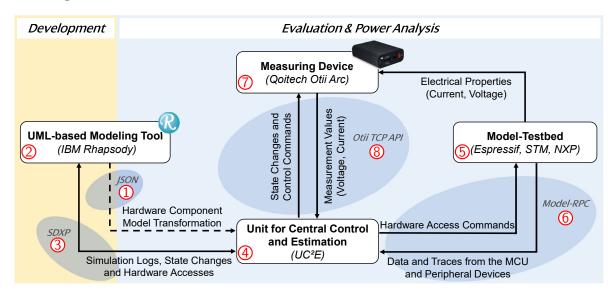

- The *Indirect Power Analysis (IPA)* method provides a simulation-based rapid power analysis with a virtual hardware platform based on hardware models. This method may be used to test software application models without physical hardware, for example, in early development phases.

- The *Direct Power Analysis (DPA)* method, a superset of IPA, defines a novel in-the-loop testing approach and utilizes a physical embedded system (testbed) for the estimation process. To achieve an early power consumption estimation, DPA and IPA are based on the same set of communication protocols and a centralized tool to simulate hardware components (IPA) and to enable communication between the software application model and the testbed (DPA) during simulation. With DPA, software application models executed within a simulation environment can interact with the testbed to obtain, for example, real sensor data.

- A case study of an IoT application for a beehive microclimate sensor node as a proofof-concept intended to demonstrate the applicability and potential of the overall power consumption estimation approach. The proof-of-concept includes the specification of

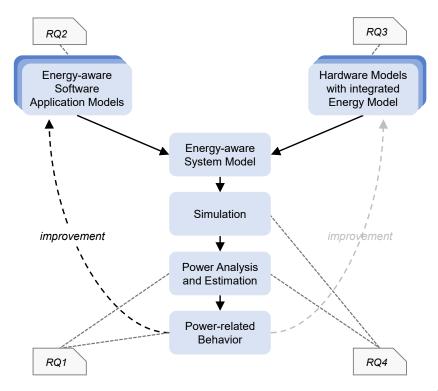

Figure 1.1: Framing and associated RQs of this thesis. Notation according to [197, 198].

software and hardware models, the elaboration of scenarios, and the definition of energyrelated NFRs. By this, the provided case study also contributes to the evaluation of RQ1 and RQ3.

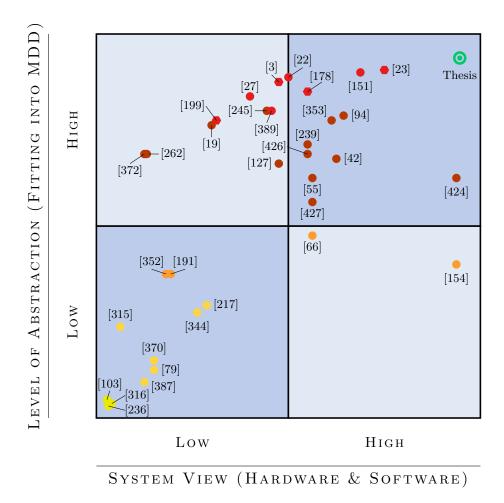

Figure 1.1 sketches the overall approach depicted as a Y-chart<sup>2</sup> with associated RQs as notes. For example, contributions to answer RQ1 provide fundamental concepts for the power analysis process, which may be used to improve software application models. Note that the improvement of hardware models may also be achieved but is not in the scope of the presented thesis. Software models may become energy aware when contributions to address RQ2 are applied. Hardware models are defined by concepts resulting from answering RQ3 and are combined with the energy-aware software model into a system model. Contributions to address RQ4 cover parts of the simulation and the power analysis concept to achieve early power consumption estimation.

The introduced contributions to answer RQ1 to RQ4 have been part of different publications. The following Table 1.1 contains a list of core publications addressing the four presented RQs. A complete list of related publications that resulted from this thesis is presented in Chapter *Publications* (p. 243 ff.).

$<sup>^{2}</sup>$ The term Y-chart refers to the shape of the diagram and is not related to the well-known representation to visualize design views and hierarchies introduced by Gajski and Kuhn (1983) [130].

| Publication Title                                                                                                                 | RQ1          | RQ2          | RQ3          | RQ4          |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|--------------|

| As Lead Author                                                                                                                    |              |              |              |              |

| Framework of software design patterns for energy-aware embedded systems. [337]                                                    |              | $\checkmark$ |              |              |

| Energy-aware pattern framework: The energy-efficiency challenge for<br>embedded systems from a software design perspective. [338] |              | $\checkmark$ |              |              |

| Power consumption estimation in model driven software development for<br>embedded systems. [339]                                  |              |              | $\checkmark$ | $\checkmark$ |

| Towards power consumption optimization for embedded systems from a<br>model-driven software development perspective. [340]        |              |              | $\checkmark$ | $\checkmark$ |

| Hunting energy bugs in embedded systems: A software-model-in-the-loop approach. [341]                                             | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |

| As Co-Author with equal contributions                                                                                             |              |              |              |              |

| Rapid-prototyping and early validation of software models through<br>uniform integration of hardware [393]                        |              |              |              | $\checkmark$ |

| PowerMonitor: Design pattern for modeling energy-aware embedded<br>systems: Work-in-progress. [392]                               |              | $\checkmark$ |              |              |

| Software design of energy-aware peripheral control for sustainable internet-of-things devices. [391]                              |              |              | $\checkmark$ |              |

Table 1.1: Relationship between core publications and introduced RQs.

# **1.3** Limitations

This thesis aims to provide novel approaches for the estimation of power consumption as well as the description of energy-aware software design patterns. The introduced concepts of energy bugs, scenarios, and energy-aware software design patterns are specified at a high level of abstraction. Therefore they can be extended, modified, and applied to other domains. However, the power consumption estimation concept has more specific requirements. To provide a proof-of-concept, the presented work is limited in several areas:

- *Type of embedded systems*: We target software application models for embedded systems, especially IoT devices with limited resources and computing power that collect data and send information using specific wireless communication protocols. We specifically do not consider high-performance computing or desktop applications, desktop and server systems, and distributed systems with intensive network communication. The presented concept may be applied to the aforementioned domains. However, no feasibility studies have been conducted on this topic. Additionally, it is not in the scope of this thesis to provide a network simulator.

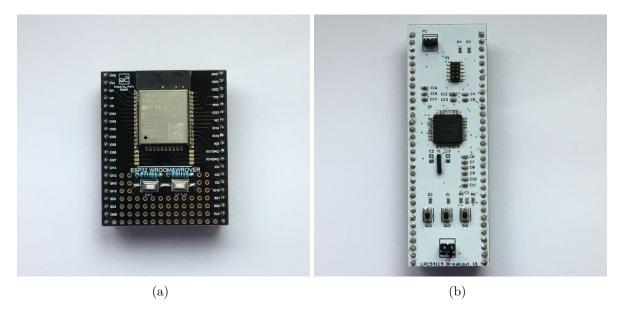

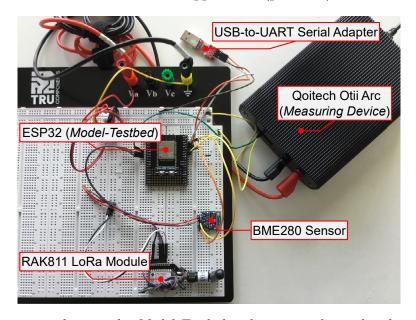

- *MCU Support*: Another limitation is the support for different MCUs. As an executing platform for the evaluation process, we have developed three prototypes based on the Espressif Systems ESP32 [111], NXP LPC54114 [269], and STMicroelectronics STM32L476 [371] MCUs specifically designed for power measurement and rapid prototyping. The software has been ported for all three platforms. However, the proof-of-concept

#### 1.3. LIMITATIONS

presented in this thesis does not aim to provide a direct comparison between or a detailed performance analysis of these MCUs.

- *Modeling Languages*: As the most widely used modeling language in the embedded software industry [7], UML is used to specify models of software applications and hardware components. The concepts presented in this thesis may be applied to other modeling languages providing mechanisms for extending models and describing NFPs. First results for the adaptation of the proposed approach to enable functional testing in Math-Works Matlab/Simulink were submitted as new research and accepted as a scientific publication [393].

- Quality of Hardware Components Models: The power consumption estimation process can only be as good as the models used in the estimation process. Generally, the quality of a hardware model depends on multiple factors, e.g., the availability of data sheets, measuring instruments, and the experience of developers. However, the introduced power estimation approach is limited if a hardware component to be modeled has at least one or more of the following properties:

- Black Box Model and Behavior: If hardware components are described as a black box, the power-related behavior can only be deduced from observations, whereby it is not always clear which operations lead to a changed power-related behavior. Additionally, if the current state of the component cannot be queried or determined, the present concept can only assume the expected behavior during a simulation. However, assumptions can lead to significant differences and inaccuracies in the power consumption estimation process.

- Environmental Impact: The presented concepts in this thesis are not designed to include (randomly occurring) environmental effects in the estimation process, leading to a change in the power-related behavior of hardware components. This thesis introduces the concept of scenarios to define a subset of possible environmental impacts for specific use cases. To fully include the effect of the surrounding, an environmental model and simulator or a highly specific laboratory environment are necessary to control, for example, interference in wireless communications or particle changes in the air during simulation. However, such approaches may be coupled with the presented concepts.

Additionally, power-saving techniques such as Dynamic Voltage and Frequency Scaling (DVS) and Dynamic Voltage Scaling (DVFS) may, theoretically, also be modeled abstractly but are also not in the scope of this thesis.

• Code Generation and Optimization: The thesis aims to estimate power consumption in early development phases. This also includes stages in which the hardware platform is not defined, currently being evaluated, or only partially available. The concepts in this thesis are focused on behavioral and architectural aspects of software application models and not on the characteristics of specific programming languages. However, according to the MDD methodology, the hardware-specific source code of such software applications models is obtained by automatic code generation techniques provided, e.g., by MDD tools. In order to be independent of programming languages, our approach is limited to the simulation of software application models, while source code generation or power-related optimizations on the source code level are not considered.

# 1.4 Thesis Outline

This section outlines the remaining structure of the thesis. Related topics have been grouped thematically into individual chapters to enhance the readability and the common thread. Unless stated otherwise, the color coding in figures presented in the following chapters enhances the illustration and has no semantic meaning. Figures without references in their caption were developed by the author.

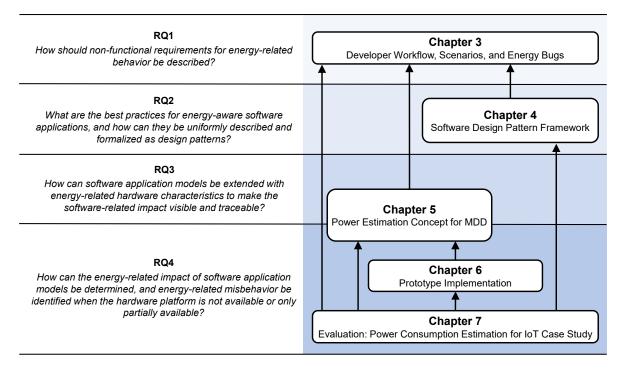

Figure 1.2: Relations between main chapters with addressed research questions. Arrows indicate usage relationships.

Figure 1.2 provides a graphical overview of the relations between the main chapters of this thesis and their associated RQs. Each chapter focuses on one RQ but may also contribute to answering additional RQs. The remainder of this thesis is organized as follows:

Chapter 2 (p. 17 ff.) presents related work and background closely related to the challenges and contributions of this thesis. This includes background in the field of software and systems engineering, including electrical power measurement, embedded systems, embedded software, IoT, requirements engineering, and MDD. Related work is discussed on energy bugs, software design patterns and their correlation to power and energy consumption, the integration of virtual and physical hardware devices, and power consumption modeling and estimation. To further enhance the understanding of methodological, technological, and design choices, this chapter concludes with an additional section to summarize findings and remarks.

**Chapter 3** (p. 77 ff.) outlines the overall approach of this thesis and describes how the presented concepts are related and interconnected. In addition, this chapter introduces the basic concepts of scenarios and energy bugs as contributions to answering RQ1, which form the basis for other concepts in subsequent chapters of the thesis.

**Chapter 4** (p. 89 ff.) presents the software design pattern framework for identifying and describing energy-aware software design patterns. To overcome RQ2, the framework describes the design pattern identification process and introduces a novel design pattern template. This chapter also provides the first energy-aware design pattern catalog, containing five design patterns reusing existing solutions and one newly developed design pattern. All energy-aware design patterns are uniformly described with the presented design pattern template.

Chapter 5 (p. 115 ff.) introduces the power consumption estimation concept for software applications models in MDD to answer RQ3 and parts of RQ4. In addition to the presentation of the concept vision, this chapter describes the hardware modeling process and introduces a UML profile to model power-related aspects as contributions to address RQ3. To answer parts of RQ4, two power analysis methods are proposed.

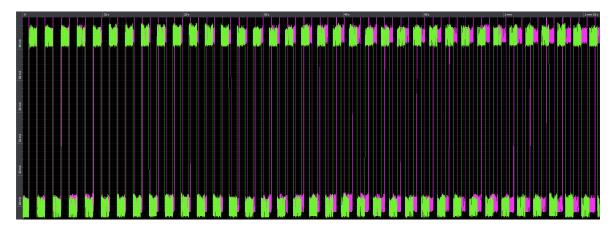

**Chapter 6** (p. 139 ff.) introduces a prototype implementation of the power estimation methods presented in Chapter 5 as a proof-of-concept. The implementation also includes the development of a policy-oriented *Hardware Abstraction Layer (HAL)*, an external and independent estimation tool, communication protocols, and a set of hardware platforms for the power estimation of system models during simulation.

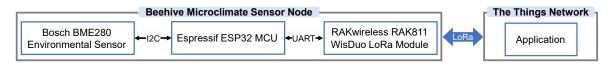

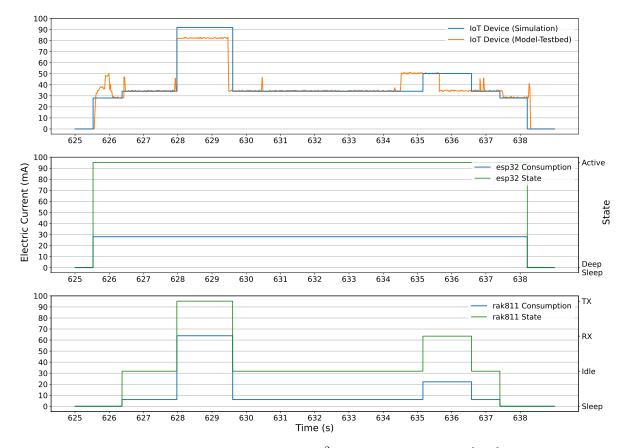

**Chapter 7** (p. 175 ff.) provides the evaluation of the power consumption estimation approach based on the prototype implementation introduced in Chapter 6. A case study of a beehive microclimate sensor IoT node example illustrates the application of the modeldriven concepts introduced in Chapter 5. The case study covers the definition of hardware component models in UML for each component of the sensor node and also demonstrates the use of the PAP UML profile to model static and dynamic power-related NFPs. Besides the case study evaluation, the overall performance of the power estimations method with a connected hardware platform is discussed.

Finally, **Chapter 8** (p. 197 ff.) concludes this thesis and summarizes the contributions and findings to overcome the introduced RQs. This chapter also provides a conclusion of this thesis and an outlook with open and new ideas for future research.

# Chapter 2

# **Related Work and Background**

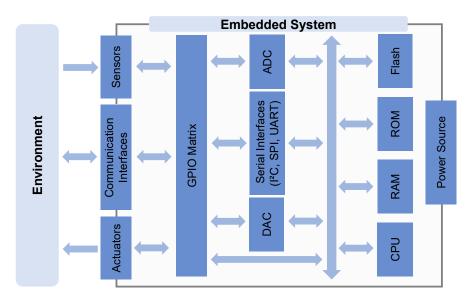

This chapter presents the related work and background regarding the proposed concepts and approaches to increase the understanding of this thesis. Since the proposed contributions consider and combine various fields to answer RQ1 to RQ4, the related work and background presented in this chapter cover a wide range of topics. An outline of electrical power measurement fundamentals, metrics, and techniques are presented in Section 2.1. Section 2.2 presents an overview of embedded systems, embedded software applications, and IoT as the basis for the case study presented in Chapter 7 (p. 175 ff.). Aspects of requirements engineering are discussed in Section 2.3. An overview of pattern descriptions and related work on patterns with correlation to power and energy consumption are provided in Section 2.4. Section 2.5 introduces concepts of MDD, while Section 2.6 covers selected aspects of MARTE as a basis UML profile to model non-functional aspects. Section 2.7 gives an overview of software testing principles. Finally, Section 2.9 discusses further findings and remarks, as well as technology and design decisions based on the presented work.

# 2.1 Electrical Power Measurement

This section presents the physical background on topics related to electrical power, electrical energy, and power consumption measuring techniques. The topics in this section provide basics for modeling power- and energy-related requirements and properties and for measuring embedded systems as part of the power estimation process.

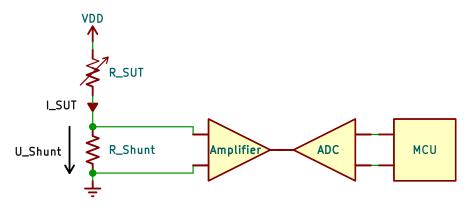

Section 2.1 briefly introduces the terminology and fundamentals of voltage and electric current, as well as power and energy as characteristics of hardware components used, for example, in embedded systems as described in Section 2.2 (p. 21 ff.). Metrics based on the introduced fundamentals, which can be used for requirement evaluation within the concepts presented in Chapter 5 (p. 115 ff.), are covered in Section 2.1.2. Section 2.1.3 discusses different power measurement techniques along with their advantages and disadvantages.

#### 2.1.1 Physical Fundamentals

The first term introduced is the electric charge (Q), which defines a property of matter. It is responsible for a certain force that the matter experiences in an electromagnetic field. The unit of electric charge is defined as coulomb (C). The electric charge can be positive or negative and is carried by subatomic particles, for example, as the elementary charge of an electron which is ~  $1.602 \cdot 10^{-19} C$ . An electric field is a structure that surrounds electrically charged elements. Electric potential refers to the amount of work needed, e.g., energy, to move a unit of electric charge Q from one point in the direction of another point within the electric field. The unit of electric potential is volt (V), which is equal to  $J \cdot C^{-1}$ , and describes the ratio between potential energy in joules (J) and electric charge in coulomb (C).

Voltage, denoted as U, can be described as the difference in electric potential between two points and, thus, as the quantitative measure of the potential difference. Electric current, also referred to as current in this thesis, is defined as  $Q \cdot t^{-1}$  and defines the flow of the electric charge Q across an electrical conductor or space at the rate of one C during an interval of time t. As stated by Ohm's law, the electric current between two points in a conductor is directly proportional to voltage. The electric current is formally denoted as I and measured in ampere (A).

Electric power, denoted as P and also known as power consumption, describes the rate at which an electric circuit transfers electrical energy. For non-constant parts whose characteristics may vary over time, the electric power P is defined as:

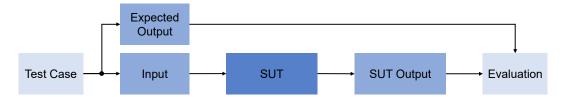

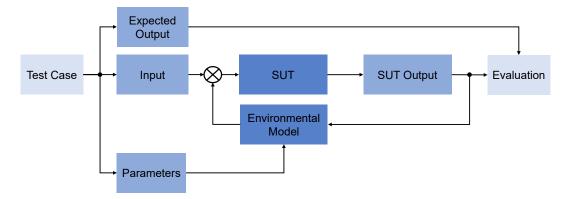

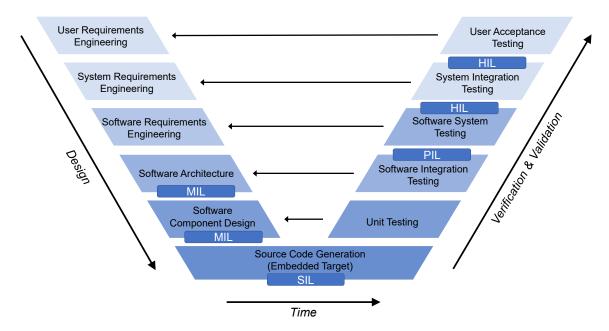

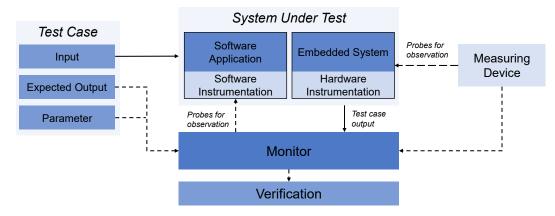

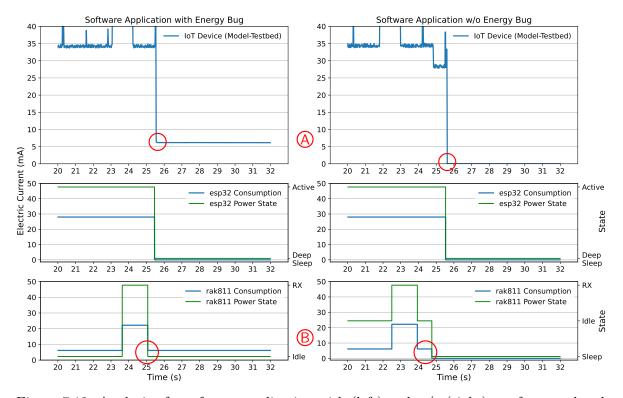

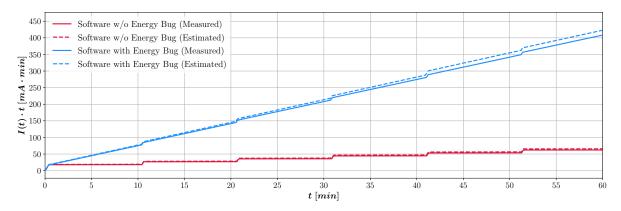

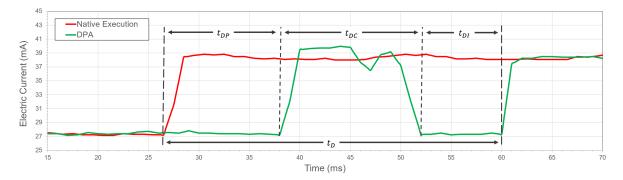

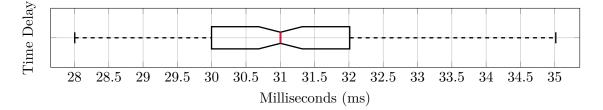

$$P(t) = U(t) \cdot I(t) \tag{2.1}$$